# LT7182S

# PMBus/I<sup>2</sup>C Reference Manual

## **OVERVIEW**

This reference manual describes the digital communications capabilities of the LT®7182S, including the functionality of each LT7182S PMBus command. Please refer to the following specifications for more information regarding bus protocol details.

- PMBus Specification Revision 1.3.1

- SMBus Specification Revision 3.1

## PMBus/SMBus/I<sup>2</sup>C CAPABILITIES

The LT7182S serial interface is PMBus compliant and can operate at any frequency between 10kHz and 1MHz. The device address is configurable using the EEPROM and/ or a configuration resistor on ASEL. The serial interface supports the following protocols defined in the PMBus and SMBus specifications.

- Send Byte, Write Byte, Write Word, Block Write

- Read Byte, Read Word, Block Read

- Alert Response Address

- PAGE\_PLUS\_READ, PAGE\_PLUS\_WRITE

- Zone Write

- SMBALERT MASK Read and Write

The LT7182S pulls the ALERT pin low to indicate conditions that may require attention. Please see the Status section in PMBus Command Details section for more information.

# SIMILARITY BETWEEN PMBus, SMBus AND I<sup>2</sup>C 2-WIRE INTERFACE

The PMBus 2-wire interface is an incremental extension of the SMBus. SMBus is built upon I<sup>2</sup>C with some minor differences in timing, DC parameters and protocol. The PMBus/SMBus protocols are more robust than simple I<sup>2</sup>C byte commands because PMBus/SMBus provide timeouts to prevent persistent bus errors and optional packet error checking (PEC) to ensure data integrity. In general,

a bus controller device that can be configured for I<sup>2</sup>C communication can be used for PMBus communication with little or no change to hardware or firmware. Repeat start (restart) is not supported by all I<sup>2</sup>C controllers but is required for SMBus/PMBus reads. If a general purpose I<sup>2</sup>C controller is used, please check that repeat start is supported.

For a description of the minor extensions and exceptions PMBus makes to SMBus, refer to PMBus Specification Part 1 Revision 1.3.1: Section 5: Transport.

For a description of the differences between SMBus and  $I^2C$ , refer to System Management Bus (SMBus) Specification Version 3.1: Appendix B—Differences Between SMBus and  $I^2C$ .

#### **COMMUNICATION PROTECTION**

All read operations will return a valid PEC if the PMBus controller requests it. If bit 2 of the MFR\_CONFIG\_ALL\_LT7182S command is set, the PMBus write operations will not be acted upon until a valid PEC has been received by the LT7182S. If a PEC is included in a command write, that PEC must be valid or a PEC write error will occur, regardless of the value of bit 2 of the MFR CONFIG ALL LT7182S command.

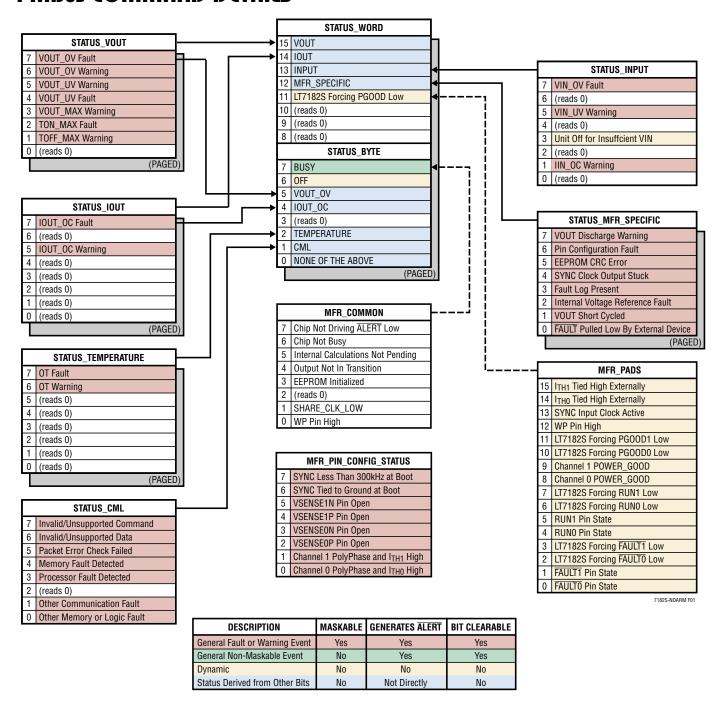

If a PEC write error occurs, an attempt is made to access unsupported commands, or invalid data is written to supported commands, then the LT7182S ignores the command, sets the CML bit in the STATUS\_BYTE and STATUS\_WORD commands, sets the appropriate bit in the STATUS\_CML command, and pulls the ALERT pin low.

#### **DEVICE ADDRESSING**

The LT7182S offers addressing modes that provide flexible ways to control multiple channels at once as well as individually.

Device addressing is the standard way to communicate with a single instance of the LT7182S. The value of the

All registered trademarks and trademarks are the property of their respective owners.

### **OVERVIEW**

device address is set by a combination of the ASEL configuration pin and the MFR\_ADDRESS command. Device addressing can be disabled by writing a value of 0x80 to the MFR\_ADDRESS. Individual channels are accessed using the PAGE command to select the desired channel, or by using the PMBus PAGE\_PLUS command. If MFR\_ADDRESS cannot be read from NVM due to an NVM fault, the device address will be set to 0x7C.

Global addressing provides a means to address all LT7182S devices on the bus. The LT7182S global addresses are fixed at 0x5A (7-bit notation) and 0x5B. They cannot be disabled. Commands sent to the 0x5A global address act the same as if PAGE is set to a value of 0xFF. Commands sent are written to both channels simultaneously. Global address 0x5B is paged and allows channel specific command of all LT7182S devices on the bus. Do not read from global addresses, as multiple devices may respond simultaneously. Other ADI device types may respond at one or both of these global addresses.

Rail addressing provides a means to control multiple channels connected together to produce a single output voltage (PolyPhase®). While similar to global addressing, the rail address can be dynamically assigned with the paged MFR\_RAIL\_ADDRESS command, allowing for any logical grouping of channels that might be required for reliable system control. Do not read from rail addresses since multiple ADI devices may respond.

Zone write addressing provides a means to write to a set of channels. The set of channels may be distributed across multiple devices. Each channel is programmed to be part of a zone by programming the selected zone number to the ZONE\_CONFIG command for that page. This configuration only needs to be performed once. After zone configuration, the bus controller uses the ZONE\_ACTIVE command to select the active zone. If a channel's configured zone matches the active zone, or the active zone is set to the "All Zone", the channel will respond to subsequent ZONE\_WRITE operations. A ZONE\_WRITE operation is started when the bus controller uses the ZONE\_WRITE address (0x37, 7-bit notation) as the device address in an SMBus write command.

All means of PMBus addressing require the user to employ disciplined planning to avoid addressing conflicts. Communication to LT7182S devices at global and rail addresses should be limited to command write operations.

#### COMMUNICATION RECOMMENDATIONS

If PMBus commands are received faster than they are being processed, the part may become too busy to handle new commands. If a command is written when the device is busy processing a command, the device will ignore that command, set bit 7 of STATUS\_BYTE and pull the ALERT pin low. MFR\_COMMON bit 6 will be set to a 1 when the device is ready to accept commands. This bit may be polled before writing commands. Alternatively, clock stretching may be enabled. Clock stretching is enabled by setting bit 1 of MFR\_CONFIG\_ALL\_LT7182S.

NVM commands may take longer to process, including STORE\_USER\_ALL, MFR\_COMPARE\_USER\_ALL, and MFR\_FAULT\_LOG\_CLEAR. When writing repeated VOUT\_MAX or MFR\_PWM\_MODE\_LT7182S commands to both channels simultaneously at bus speeds above 400kHz, the device may also become too busy to respond immediately. In these cases, either poll MFR\_COMMON bit 6 or enable clock stretching to avoid a busy condition.

Table 1 list supported PMBus commands and manufacturer specific commands. A complete description of the included PMBus commands can be found in the PMBus Power System Management Protocol Specification. Floating point values listed in the "DEFAULT VALUE" column are half-precision IEEE floating point numbers. If MFR CONFIG ALL is used to disable IEEE floating point mode, all floating point commands will read and write values using either Linear11 or ULinear16 format, as indicated by the DATA FORMAT column in Table 1. Please see Table 2 for data format details. All commands from 0xC0 through 0xFF not listed in Table 1 are implicitly reserved by the manufacturer. Users should avoid blind writes within this range of commands to avoid undesired operation of the part. All commands from 0x00 through 0xBF not listed in Table 1 are implicitly not supported by the manufacturer. Attempting to access non-supported or reserved commands may result in a CML command fault event.

Rev. 0

## TABLE OF CONTENTS

| Overview                                             |    |

|------------------------------------------------------|----|

| PMBus/SMBus/I <sup>2</sup> C Capabilities            | 1  |

| Similarity Between PMBus, SMBus and I <sup>2</sup> C |    |

| 2-Wire Interface                                     | 1  |

| Communication Protection                             | 1  |

| Device Addressing                                    | 1  |

| Communication Recommendations                        |    |

| PMBus Command Summary                                |    |

| PMBus Command Details                                | 9  |

| Addressing and Write Protect                         |    |

| General Configuration                                |    |

| Pwm Configuration                                    | 18 |

| MFR_SYNC_CONFIG_LT7182S                              |    |

| Input Voltage and Limits                             |    |

| Output Voltage and Limits                            | 22 |

| Input Current Limits                                 |    |

| Output Current Limits                                | 27 |

| Temperature                                          | 28 |

| Timing          | 29 |

|-----------------|----|

| Sequencing On   |    |

| Sequencing Off  | 30 |

| Restarting      |    |

| Fault Response  | 33 |

| All Faults      | 33 |

| Input Voltage   | 33 |

| Output Voltage  | 34 |

| Output Current  |    |

| Temperature     | 38 |

| Fault Sharing   | 38 |

| Identification  |    |

| Status          | 40 |

| Telemetry       | 48 |

| NVM Commands    | 51 |

| FAULT Logging   |    |

| Event Structure | 55 |

| Evample Evant   | 50 |

**Table 1. PMBus Command Summary Table**

| COMMAND NAME         | CMD<br>CODE | ID DE DESCRIPTION                                                           |                          | PAGED | DATA<br>Format | UNITS | EEPROM | DEFAULT<br>Value                             |

|----------------------|-------------|-----------------------------------------------------------------------------|--------------------------|-------|----------------|-------|--------|----------------------------------------------|

| PAGE                 | 0x00        | Provides integration with multi-page PMBus devices.                         | with multi-page R/W Byte |       | Reg            |       |        | 0x00                                         |

| OPERATION            | 0x01        | Operating mode control. On/off, margin high and margin low.                 | R/W<br>Byte              | Υ     | Reg            |       | Y      | 0x80                                         |

| ON_OFF_CONFIG        | 0x02        | RUN pin and PMBus bus on/off command configuration.                         | R/W<br>Byte              | Υ     | Reg            |       | Y      | 0x1E                                         |

| CLEAR_FAULTS         | 0x03        | Clear any fault bits that have been set.                                    | Send<br>Byte             | N     |                |       |        |                                              |

| PAGE_PLUS_WRITE      | 0x05        | Write a command directly to a specified page.                               | W<br>Block               | N     |                |       |        |                                              |

| PAGE_PLUS_READ       | 0x06        | Read a command directly from a specified page.                              | Block<br>R/W             | N     |                |       |        |                                              |

| ZONE_CONFIG          | 0x07        | Assigns current page to specified zone number for ZONE_WRITE operations.    | W<br>Word                | Υ     | Reg            |       | Y      | 0xFEFE                                       |

| ZONE_ACTIVE          | 0x08        | Selects active zone for ZONE_WRITE operations.                              | W<br>Word                |       | Reg            |       |        | 0xFEFE                                       |

| WRITE_PROTECT        | 0x10        | Level of protection provided by the device against accidental changes.      | R/W<br>Byte              | N     | Reg            |       | Y      | 0x00                                         |

| STORE_USER_ALL       | 0x15        | Store user operating memory to EEPROM.                                      | Send<br>Byte             | N     |                |       |        |                                              |

| RESTORE_USER_ALL     | 0x16        | Restore user operating memory from EEPROM.                                  | Send<br>Byte             | N     |                |       |        |                                              |

| CAPABILITY           | 0x19        | Summary of PMBus optional communication protocols supported by this device. | R<br>Byte                | N     | Reg            |       |        | 0xD8                                         |

| QUERY                | 0x1A        | Asks if a given command is supported, and what data formats are supported.  | Block<br>R/W             | N     | Reg            |       |        |                                              |

| SMBALERT_MASK        | 0x1B        | Masks ALERT activity.                                                       | Block<br>R/W             | Y     | Reg            |       | Y      |                                              |

| VOUT_MODE            | 0x20        | Output voltage format and exponent.                                         | R<br>Byte                | N     | Reg            |       |        | 0x60                                         |

| VOUT_COMMAND         | 0x21        | Nominal output voltage set point.                                           | R/W<br>Word              | Υ     | IEEE/<br>UL16  | V     | Y      | 0.5<br>0x3800                                |

| VOUT_MAX             | 0x24        | Upper limit on the commanded output voltage.                                | R/W<br>Word              | Υ     | IEEE/<br>UL16  | V     | Y      | 0.537<br>0x384C                              |

| VOUT_MARGIN_HIGH     | 0x25        | Margin high output voltage set point.                                       | R/W<br>Word              | Υ     | IEEE/<br>UL16  | V     | Y      | 0.525<br>0x3833                              |

| VOUT_MARGIN_LOW      | 0x26        | Margin low output voltage set point.                                        | R/W<br>Word              | Υ     | IEEE/<br>UL16  | V     | Y      | 0.475<br>0x379A                              |

| /OUT_TRANSITION_RATE | 0x27        | Rate the output changes when V <sub>OUT</sub> commanded to a new value.     | R/W<br>Word              | Υ     | IEEE/L11       | V/ms  | Y      | 0.25<br>0x3400                               |

| FREQUENCY_SWITCH     | 0x33        | Switching frequency of the regulator.                                       | R/W<br>Word              | N     | IEEE/L11       | kHz   | Y      | 1000.0<br>0x63D0                             |

| VIN_ON               | 0x35        | Input voltage at which the unit should start power conversion.              | R/W<br>Word              | Y     | IEEE/L11       | V     | Y      | Ch. 0: 1.5<br>0x3E00<br>Ch. 1: 1.4<br>0x3D9A |

**Table 1. PMBus Command Summary Table**

| COMMAND NAME           | CMD<br>CODE | DESCRIPTION                                                                                           | ТҮРЕ        | PAGED | DATA<br>Format | UNITS | EEPROM | DEFAULT<br>Value                               |

|------------------------|-------------|-------------------------------------------------------------------------------------------------------|-------------|-------|----------------|-------|--------|------------------------------------------------|

| VIN_OFF                | 0x36        | Input voltage at which the unit should stop power conversion.                                         | R/W<br>Word | Y     | IEEE/L11       | V     | Y      | Ch. 0: 1.45<br>0x3DCD<br>Ch. 1: 1.35<br>0x3D66 |

| VOUT_OV_FAULT_LIMIT    | 0x40        | Output overvoltage fault limit.                                                                       | R/W<br>Word | Y     | IEEE/L11       | V     | Y      | 0.55<br>0x3866                                 |

| VOUT_OV_FAULT_RESPONSE | 0x41        | Action to be taken by the device when an output overvoltage fault is detected.                        | R/W<br>Byte | Υ     | Reg            |       | Y      | 0xB8                                           |

| VOUT_OV_WARN_LIMIT     | 0x42        | Output overvoltage warning limit.                                                                     | R/W<br>Word | Υ     | IEEE/L11       | V     | Y      | 0.537<br>0x384C                                |

| VOUT_UV_WARN_LIMIT     | 0x43        | Output undervoltage warning limit.                                                                    | R/W<br>Word | Υ     | IEEE/L11       | V     | Y      | 0.467<br>0x3779                                |

| VOUT_UV_FAULT_LIMIT    | 0x44        | Output undervoltage fault limit.                                                                      | R/W<br>Word | Y     | IEEE/L11       | V     | Y      | 0.465<br>0x3771                                |

| VOUT_UV_FAULT_RESPONSE | 0x45        | Action to be taken by the device when an output undervoltage fault is detected.                       | R/W<br>Byte | Y     | Reg            |       | Y      | 0x00                                           |

| IOUT_OC_FAULT_RESPONSE | 0x47        | Action to be taken by the device when an output overcurrent fault is detected.                        | R/W<br>Byte | Υ     | Reg            |       | Y      | 0x00                                           |

| IOUT_OC_WARN_LIMIT     | 0x4A        | Output overcurrent warning limit.                                                                     | R/W<br>Word | Υ     | IEEE/L11       | Α     | Y      | 8.0<br>0x4800                                  |

| OT_FAULT_LIMIT         | 0x4F        | Internal overtemperature fault limit.                                                                 | R/W<br>Word | N     | IEEE/L11       | С     | Y      | 160.0<br>0x5900                                |

| OT_FAULT_RESPONSE      | 0x50        | Action to be taken by the device when an external overtemperature fault is detected.                  | R/W<br>Byte | N     | Reg            |       | Y      | 0xC0                                           |

| OT_WARN_LIMIT          | 0x51        | Internal overtemperature warning limit.                                                               | R/W<br>Word | N     | IEEE/L11       | С     | Y      | 140.0<br>0x5860                                |

| VIN_OV_FAULT_RESPONSE  | 0x56        | Action to be taken by the device when an input overvoltage fault is detected.                         | R/W<br>Byte | Υ     | Reg            |       | Y      | 0xB8                                           |

| VIN_UV_WARN_LIMIT      | 0x58        | Input supply undervoltage warning limit.                                                              | R/W<br>Word | Υ     | IEEE/L11       | V     | Y      | -1.0<br>0xBC00                                 |

| IIN_OC_WARN_LIMIT      | 0x5D        | Input supply overcurrent warning limit.                                                               | R/W<br>Word | Υ     | IEEE/L11       | Α     | Y      | 8.0<br>0x4800                                  |

| TON_DELAY              | 0x60        | Time from RUN and/or Operation on to output rail turn-on.                                             | R/W<br>Word | Υ     | IEEE/L11       | ms    | Y      | 0.0<br>0x0000                                  |

| TON_RISE               | 0x61        | Time from when the output starts to rise until the output voltage reaches the VOUT commanded value.   | R/W<br>Word | Υ     | IEEE/L11       | ms    | Y      | 1.0<br>0x3C00                                  |

| TON_MAX_FAULT_LIMIT    | 0x62        | Maximum time from the start of TON_RISE for VOUT to cross the VOUT_UV_FAULT_LIMIT.                    | R/W<br>Word | Υ     | IEEE/L11       | ms    | Y      | 5.0<br>0x4500                                  |

| TON_MAX_FAULT_RESPONSE | 0x63        | Action to be taken by the device when a TON_ MAX_FAULT event is detected.                             | R/W<br>Byte | Υ     | Reg            |       | Y      | 0x00                                           |

| TOFF_DELAY             | 0x64        | Time from RUN and/or Operation off to the start of TOFF_FALL ramp.                                    | R/W<br>Word | Υ     | IEEE/L11       | ms    | Y      | 0.0<br>0x0000                                  |

| TOFF_FALL              | 0x65        | Time from when the output starts to fall until the output reaches zero volts.                         | R/W<br>Word | Υ     | IEEE/L11       | ms    | Y      | 2.0<br>0x4000                                  |

| TOFF_MAX_WARN_LIMIT    | 0x66        | Maximum allowed time, after TOFF_FALL completed, for the unit to decay below MFR_DISCHARGE_THRESHOLD. | R/W<br>Word | Y     | IEEE/L11       | ms    | Y      | 0.0<br>0x0000                                  |

**Table 1. PMBus Command Summary Table**

| COMMAND NAME        | CMD<br>CODE | DESCRIPTION                                                          | ТҮРЕ        | PAGED | DATA<br>Format | UNITS | EEPROM | DEFAULT<br>Value |

|---------------------|-------------|----------------------------------------------------------------------|-------------|-------|----------------|-------|--------|------------------|

| STATUS_BYTE         | 0x78        | One byte summary of the unit's fault condition.                      | R/W<br>Byte | Υ     | Reg            |       |        |                  |

|                     |             | Two byte summary of the unit's fault condition.                      | R/W<br>Word | Y     | Reg            |       |        |                  |

| STATUS_VOUT         | 0x7A        | Output voltage fault and warning status.                             | R/W<br>Byte | Υ     | Reg            |       |        |                  |

| STATUS_IOUT         | 0x7B        | Output current fault and warning status.                             | R/W<br>Byte | Υ     | Reg            |       |        |                  |

| STATUS_INPUT        | 0x7C        | Input supply fault and warning status.                               | R/W<br>Byte | Υ     | Reg            |       |        |                  |

| STATUS_TEMPERATURE  | 0x7D        | Internal temperature fault and warning status for READ_TEMERATURE_1. | R/W<br>Byte | N     | Reg            |       |        |                  |

| STATUS_CML          | 0x7E        | Communication and memory fault and warning status.                   | R/W<br>Byte | N     | Reg            |       |        |                  |

| STATUS_MFR_SPECIFIC | 0x80        | Manufacturer specific fault and state information.                   | R/W<br>Byte | Υ     | Reg            |       |        |                  |

| READ_VIN            | 0x88        | Measured input supply voltage.                                       | R<br>Word   | Υ     | IEEE/L11       | V     |        |                  |

| READ_IIN            | 0x89        | Measured input supply current.                                       | R<br>Word   | Υ     | IEEE/L11       | Α     |        |                  |

| READ_VOUT           | 0x8B        | Measured output voltage.                                             | R<br>Word   | Υ     | IEEE/<br>UL16  | V     |        |                  |

| READ_IOUT           | 0x8C        | Measured output current.                                             | R<br>Word   | Υ     | IEEE/L11       | Α     |        |                  |

| READ_TEMPERATURE_1  | 0x8D        | Measured internal temperature.                                       | R<br>Word   | N     | IEEE/L11       | С     |        |                  |

| READ_FREQUENCY      | 0x95        | Measured PWM switching frequency.                                    | R<br>Word   | Υ     | IEEE/L11       |       |        |                  |

| READ_POUT           | 0x96        | Calculated output power.                                             | R<br>Word   | Υ     | IEEE/L11       |       |        |                  |

| PMBUS_REVISION      | 0x98        | PMBus revision supported by this device. Current revision is 1.3.    | R<br>Byte   | N     | Reg            |       |        | 0x33             |

| MFR_ID              | 0x99        | The manufacturer ID in ASCII.                                        | R<br>Block  | N     |                |       |        | "ADI"            |

| MFR_MODEL           | 0x9A        | The part number in ASCII.                                            | R<br>Block  | N     |                |       |        | "LT7182S"        |

| MFR_REVISION        | 0x9B        | Part revision number.                                                | R<br>Block  | N     |                |       |        |                  |

| MFR_SERIAL          | 0x9E        | Unique part serial number.                                           | R<br>Block  | N     |                |       |        |                  |

| IC_DEVICE_ID        | 0xAD        | Identification of the IC in ASCII.                                   | R<br>Block  | N     |                |       |        | "LT7182S"        |

| IC_DEVICE_REV       | 0xAE        | Revision of the IC.                                                  | R<br>Block  | N     |                |       |        |                  |

| MFR_EE_UNLOCK       | 0xBD        | Contact factory.                                                     |             |       |                |       |        |                  |

| MFR_EE_ERASE        | 0xBE        | Contact factory.                                                     |             |       |                |       |        |                  |

| MFR_EE_DATA         | 0xBF        | Contact factory.                                                     |             |       |                |       |        |                  |

**Table 1. PMBus Command Summary Table**

| COMMAND NAME                | CMD<br>CODE           | DESCRIPTION                                                                                     | ТҮРЕ         | PAGED | DATA<br>Format | UNITS | EEPROM | DEFAULT<br>Value               |

|-----------------------------|-----------------------|-------------------------------------------------------------------------------------------------|--------------|-------|----------------|-------|--------|--------------------------------|

| MFR_USER_DATA_00            | MFR_USER_DATA_00 0xC9 |                                                                                                 | R/W<br>Word  | N     | Reg            |       | Υ      | 0x0000                         |

| MFR_USER_DATA_01            | 0xCA                  | EEPROM word available for user                                                                  | R/W<br>Word  | N     | Reg            |       | Υ      | 0x0000                         |

| MFR_USER_DATA_02            | 0xCB                  | EEPROM word available for user                                                                  | R/W<br>Word  | N     | Reg            |       | Y      | 0x0000                         |

| MFR_USER_DATA_03            | 0xCC                  | EEPROM word available for user                                                                  | R/W<br>Word  | N     | Reg            |       | Y      | 0x0000                         |

| MFR_READ_EXTVCC             | 0xCD                  | Measured EXTVCC voltage, when enabled                                                           | R<br>Word    | N     | IEEE/L11       | V     |        |                                |

| MFR_READ_ITH                | 0xCE                  | Measured I <sub>TH</sub> voltage, when enabled                                                  | R<br>Word    | Y     | IEEE/L11       | V     |        |                                |

| MFR_CHAN_CONFIG_LT7182S     | 0xD0                  | Configuration bits that are channel specific.                                                   | R/W<br>Word  | Υ     | Reg            |       | Υ      | Ch. 0: 0x00D7<br>Ch. 1: 0x0057 |

| MFR_CONFIG_ALL_LT7182S      | 0xD1                  | General configuration bits.                                                                     | R/W<br>Word  | N     | Reg            |       | Υ      | 0x0100                         |

| MFR_FAULT_PROPAGATE_LT7182S | 0xD2                  | Configuration that determines which faults are propagated to the FAULT pin.                     | R/W<br>Word  | Y     | Reg            |       | Y      | 0xE0D7                         |

| MFR_PWM_MODE_LT7182S        | 0xD4                  | Configuration for the PWM engine.                                                               | R/W<br>Word  | Y     | Reg            |       | Υ      | 0x1DD4                         |

| MFR_FAULT_RESPONSE          | 0xD5                  | Action to be taken by the device when the FAULT pin is externally asserted low.                 | R/W<br>Byte  | Υ     | Reg            |       | Υ      | 0xC0                           |

| MFR_IOUT_PEAK               | 0xD7                  | Report the maximum measured value of READ_IOUT since last MFR_CLEAR_PEAKS.                      | R<br>Word    | Y     | IEEE/L11       | А     |        |                                |

| MFR_ADC_CONTROL_LT7182S     | 0xD8                  | Configures the update rate of the measurements taken by the ADC.                                | R/W<br>Byte  | N     | Reg            |       | Y      | 0x00                           |

| MFR_RETRY_DELAY             | 0xDB                  | Retry interval during fault retry mode.                                                         | R/W<br>Word  | Y     | IEEE/L11       | ms    | Υ      | 10.0<br>0x4900                 |

| MFR_RESTART_DELAY           | 0xDC                  | Minimum time the RUN pin is held low by the LT7182S.                                            | R/W<br>Word  | Y     | IEEE/L11       | ms    | Υ      | 10.0<br>0x4900                 |

| MFR_VOUT_PEAK               | 0xDD                  | Maximum measured value of READ_<br>VOUT since last MFR_CLEAR_PEAKS.                             | R/W<br>Word  | Y     | IEEE/<br>UL16  | V     |        |                                |

| MFR_VIN_PEAK                | 0xDE                  | Maximum measured value of READ_VIN since last MFR_CLEAR_PEAKS.                                  | R/W<br>Word  | Y     | IEEE/L11       | V     |        |                                |

| MFR_TEMPERATURE_1_PEAK      | 0xDF                  | Maximum measured value of internal temperature (READ_TEMPERATURE_1) since last MFR_CLEAR_PEAKS. | R/W<br>Word  | N     | IEEE/L11       | С     |        |                                |

| MFR_CLEAR_PEAKS             | 0xE3                  | Clears all peak values.                                                                         | Send<br>Byte | N     |                |       |        |                                |

| MFR_DISCHARGE_THRESHOLD     | 0xE4                  | Output voltage used to determine output has decayed sufficiently to re-enable the channel       | R/W<br>Word  | Y     | IEEE/L11       |       | Y      | 0.2<br>0x3266                  |

| MFR_PADS_LT7182S            | 0xE5                  | Digital status of the I/O pads.                                                                 | R<br>Word    | N     | Reg            |       |        |                                |

| MFR_ADDRESS                 | 0xE6                  | Sets the 7-bit I <sup>2</sup> C address byte.                                                   | R/W<br>Word  | N     | Reg            |       | Y      | 0x4F                           |

**Table 1. PMBus Command Summary Table**

| COMMAND NAME                 | CMD<br>CODE | DESCRIPTION                                                                        | TYPE         | PAGED | DATA<br>Format | UNITS   | EEPROM | DEFAULT<br>Value                               |

|------------------------------|-------------|------------------------------------------------------------------------------------|--------------|-------|----------------|---------|--------|------------------------------------------------|

| MFR_SPECIAL_ID               | 0xE7        | ID code used by manufacturer.                                                      | R<br>Word    | N     | Reg            |         |        | 0x1C1D                                         |

| MFR_FAULT_LOG_TIMESTAMP_MSBS | 0xE8        | Sets the fault log timestamp upper 13 bits, clears lower 32 (read and write first) | R/W<br>32    | N     |                |         |        |                                                |

| MFR_FAULT_LOG_TIMESTAMP_LSBS | 0xE9        | Sets the fault log timestamp lower 32 bits.                                        | R/W<br>32    | N     |                |         |        |                                                |

| MFR_FAULT_LOG_STORE          | 0xEA        | Force a fault log entry to be written.                                             | Send<br>Byte | N     |                |         |        |                                                |

| MFR_FAULT_LOG_CLEAR          | 0xEC        | Erases all fault log entries, if any.                                              | Send<br>Byte | N     |                |         |        |                                                |

| MFR_FAULT_LOG                | 0xEE        | Read contents of fault log, if any.                                                | R<br>Block   | N     | Reg            |         |        |                                                |

| MFR_COMMON                   | 0xEF        | Manufacturer status bits that are common across multiple ADI chips.                | R<br>Byte    | N     | Reg            |         |        |                                                |

| MFR_COMPARE_USER_ALL         | 0xF0        | Compares current command contents with EEPROM.                                     | Send<br>Byte | N     |                |         |        |                                                |

| MFR_CHANNEL_STATE            | 0xF1        | Returns the state of the channel.                                                  | R<br>Byte    | Υ     | Reg            |         |        |                                                |

| MFR_PGOOD_DELAY              | 0xF2        | Time output voltage must be between UV and OV before PGOOD transitions high        | R/W<br>Word  | Y     | IEEE/L11       | ms      | Y      | 1.0<br>0x3C00                                  |

| MFR_NOT_PGOOD_DELAY          | 0xF3        | Time output voltage must be below UV or above OV before PGOOD transitions low      | R/W<br>Word  | Y     | IEEE/L11       | ms      | Y      | 0.1<br>0x2E66                                  |

| MFR_PWM_PHASE_LT7182S        | 0xF5        | Set PWM phase.                                                                     | R/W<br>Word  | Y     | IEEE/L11       | Degrees | Y      | Ch. 0: 0.0<br>0x0000<br>Ch. 1: 180.0<br>0x59A0 |

| MFR_SYNC_CONFIG_LT7182S      | 0xF6        | SYNC pin input/output configuration                                                | R/W<br>Byte  | N     | Reg            |         | Y      | 0x00                                           |

| MFR_PIN_CONFIG_STATUS        | 0xF7        | Pin configuration fault status                                                     | R<br>Byte    | N     | Reg            |         |        |                                                |

| MFR_RAIL_ADDRESS             | 0xFA        | Common address for PolyPhase outputs to adjust common parameters.                  | R/W<br>Byte  | Υ     | Reg            |         | Y      | 0x80                                           |

| MFR_DISABLE_OUTPUT           | 0xFB        | Disables regulator outputs until reset                                             | R/W<br>Byte  | N     | Reg            |         |        | 0x00                                           |

| MFR_EE_USER_WP               | 0xFC        | Disables commands that write user NVM                                              | R/W<br>Byte  | N     | Reg            |         | Y      | 0x00                                           |

| MFR_RESET                    | 0xFD        | Commanded reset without requiring a power down.                                    | Send<br>Byte | N     |                |         |        |                                                |

**Note 1:** Commands indicated with Y in the EEPROM column indicate that these commands are stored and restored using the STORE\_USER\_ALL and RESTORE\_USER\_ALL commands, respectively.

- Note 2: Commands with a default value of NA indicate "not applicable". Commands with a default value of FS indicate "factory set on a per part basis".

- **Note 3:** The LT7182S contains additional reserved commands not listed in this table. Reading these commands is harmless to the operation of the IC; however, the contents and meaning of these commands can change without notice.

- Note 4: Some of the unpublished commands are read-only and will generate a CML bit 6 fault if written.

- Note 5: Writing to commands not published in this table is not permitted.

- **Note 6:** The user should not assume compatibility of commands between different parts based upon command names. Always refer to the manufacturer's data sheet for each part for a complete definition of a command's function. ADI strives to keep command functionality compatible between all ADI devices, but differences may be introduced to address specific product requirements.

Rev. 0

**Table 2. Abbreviations of Supported Data Formats**

|      |                                              | PMBus                     |                                                                                                                                                                   |                                                                                                    |

|------|----------------------------------------------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

|      | TERMINOLOGY                                  | SPECIFICATION REFERENCE   | DEFINITION                                                                                                                                                        | EXAMPLE                                                                                            |

| L11  | Linear11                                     | Rev 1.3.1 Part II 7.3     | Floating point 16-bit data: $value = Y \cdot 2^N$ , where $N = b[15:11]$ and $Y = b[10:0]$ , both two's compliment binary integers.                               | $b[15:0] = 0x9807 = 7 \cdot 2^{-13} = 8.54 \cdot 10^4$                                             |

| UL16 | ULinear16                                    | Rev 1.3.1 Part II 8.4.1.1 | Fixed point 16-bit data: $value = Y \cdot 2^{-12}$ , where $Y = b[15:0]$ , an unsigned integer.                                                                   | $b[15:0] = 0x4C00 = 19456 \cdot 2^{-12} = 4.75$                                                    |

| Reg  |                                              |                           | Per-bit meaning defined in each command description.                                                                                                              | PMBus STATUS_BYTE command.                                                                         |

| IEEE | IEEE-754 Half<br>Precision Floating<br>Point | Rev 1.3.1 Part II 8.4.4   | Floating point 16-bit data: for normal values, $value = (-1)^{S} \cdot 2^{N-15} \cdot \left(1 + \frac{M}{1024}\right)$ where S = b[15], N = b[14:10], M = b[9:0]. | $b[15:0] = 0 \times 4580 = (-1)^{0} \cdot 2^{17-15} \cdot \left(1 + \frac{384}{1024}\right) = 5.5$ |

## PMBus COMMAND DETAILS

#### ADDRESSING AND WRITE PROTECT

| COMMAND NAME     | CODE | DESCRIPTION                                                                       | TYPE                 | PAGED | UNITS | NVM | DEFAULT |

|------------------|------|-----------------------------------------------------------------------------------|----------------------|-------|-------|-----|---------|

| PAGE             | 0x00 | Channel (page) selected for any paged command.                                    | R/W Byte             | N     |       |     | 0x00    |

| PAGE_PLUS_WRITE  | 0x05 | Write a command directly to a specified page.                                     | W Block              | N     |       |     |         |

| PAGE_PLUS_READ   | 0x06 | Read a command directly from a specified page.                                    | Block R/W<br>Process | N     |       |     |         |

| ZONE_CONFIG      | 0x07 | Specify zone number for selected page.                                            | R/W Word             | Υ     |       | Υ   | 0xFEFE  |

| ZONE_ACTIVE      | 0x08 | Sets active zone number.                                                          | R/W Word             | N     |       |     | 0xFEFE  |

| WRITE_PROTECT    | 0x10 | Protect the device from unintended PMBus modifications.                           | R/W Byte             | N     |       | Υ   | 0x00    |

| MFR_ADDRESS      | 0xE6 | Specify right-justified 7-bit device address.                                     | R/W Byte             | N     |       | Υ   | 0x4F    |

| MFR_RAIL_ADDRESS | 0xFA | Specify right-justified 7-bit address for channels comprising a PolyPhase output. | R/W Byte             | Υ     |       | Υ   | 0x80    |

#### **PAGE**

The PAGE command provides the ability to configure, control and monitor both channels through only one physical address, either the device address or global address 0x5B (7-bit address). Each PAGE contains the operating commands for one channel.

Pages 0x00 and 0x01 correspond to channel 0 and channel 1, respectively, in this device.

Setting PAGE to 0xFF applies any following paged commands to both outputs. With PAGE set to 0xFF, the device will respond to read commands as if PAGE were set to 0x00 (channel 0 results).

#### PAGE PLUS WRITE

The PAGE\_PLUS\_WRITE command provides a way to select the page within a device, send a command and then send the data for the command, all in one communication packet. Commands allowed by the present write protection level may be sent with PAGE\_PLUS\_WRITE.

The value stored in the PAGE command is not affected by PAGE\_PLUS\_WRITE. If PAGE\_PLUS\_WRITE is used to send a non-paged command, the Page Number byte is ignored.

**Note:** PAGE\_PLUS commands cannot be nested. A PAGE\_PLUS command cannot be used to read or write another PAGE\_PLUS command. If this is attempted, the device will NACK the entire PAGE\_PLUS packet and issue a CML fault for Invalid/Unsupported Data.

The PAGE\_PLUS\_WRITE command cannot be used to write the PAGE command.

If the PAGE\_PLUS\_WRITE command is sent during a ZONE\_WRITE, the page field will be used as the effective ZONE. The page field will override the write zone of ZONE\_ACTIVE for this PAGE\_PLUS\_WRITE only.

#### PAGE PLUS READ

The PAGE\_PLUS\_READ command provides the ability to select the page within a device, send a command and then read the data returned by the command, all in one communication packet.

The value stored in the PAGE command is not affected by PAGE\_PLUS\_READ. If PAGE\_PLUS\_READ is used to access data from a non-paged command, the Page Number byte is ignored.

**Note:** PAGE\_PLUS commands cannot be nested. A PAGE\_PLUS command cannot be used to read or write another PAGE\_PLUS command. If this is attempted, the device will NACK the entire PAGE\_PLUS packet and issue a CML fault for Invalid/Unsupported Data.

The PAGE\_PLUS\_READ command cannot be used to read the PAGE command.

#### **ZONE CONFIG**

The ZONE\_CONFIG command is used to assign the currently selected channel to a specific zone number for ZONE\_WRITE operations. Zone configuration only needs to be performed once, but zone numbers may be changed at any time.

A channel's zone may be assigned to any zone number between 0x00 and 0x7F. It may also be set to 0xFE, which means "No Zone". Any channel programmed to "No Zone" will ignore ZONE\_WRITE operations.

The ZONE\_CONFIG command uses the SMBus word write and word read protocols.

Table 3. ZONE CONFIG Contents

| BITS | MEANING       |

|------|---------------|

| 15-8 | Must be 0xFE  |

| 7-0  | Assigned zone |

#### **ZONE ACTIVE**

The ZONE\_ACTIVE command sets the active zone for ZONE\_WRITE operations. When a ZONE\_WRITE is sent by the bus controller, the active zone controls which channels are affected by that write.

The active zone may be set to any zone number between 0x00 and 0x7F. The active zone may also be set to 0xFF, which means "All Zone". If a ZONE\_WRITE is sent while the active zone is set to "All Zone", any channel not programmed to "No Zone" via ZONE CONFIG will be affected by that write.

The ZONE\_ACTIVE command must be sent using the ZONE\_WRITE address (0x37) as a ZONE\_WRITE operation. If the ZONE\_ACTIVE command is sent to the global, device, or rail addresses, the invalid command bit will be set in STATUS\_CML.

**Table 4. ZONE ACTIVE Contents**

| BITS | MEANING      |

|------|--------------|

| 15:8 | Must be 0xFE |

| 7:0  | Active zone  |

#### WRITE PROTECT

The WRITE\_PROTECT command is used to control writing to the device. This command does not indicate the status of the WP pin which is defined in the MFR\_COMMON command. The WP pin takes precedence over the value of this command.

If the WP pin is high, only the PAGE, OPERATION, MFR\_EE\_UNLOCK and CLEAR\_FAULTS commands are writable. individual fault bits can be cleared by writing a 1 to the respective bits in the STATUS commands.

When WRITE PROTECT is set to 0x00, writes to all commands are enabled.

PAGE\_PLUS\_WRITE may be used to write any command that is not write protected. PAGE\_PLUS\_READ may be used to read any command.

| BYTE | MEANING                                                                                                                                                                                                                                                             |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x80 | Disable all writes except to the WRITE_PROTECT, PAGE, MFR_EE_UNLOCK and STORE_USER_ALL command.                                                                                                                                                                     |

| 0x40 | Disable all writes except to the WRITE_PROTECT, PAGE, MFR_EE_UNLOCK, MFR_CLEAR_PEAKS, STORE_USER_ALL, OPERATION and CLEAR_FAULTS command. Individual fault bits can be cleared by writing a 1 to the respective bits in the STATUS registers.                       |

| 0x20 | Disable all writes except to the WRITE_PROTECT, OPERATION, MFR_EE_UNLOCK, MFR_CLEAR_PEAKS, CLEAR_FAULTS, PAGE, ON_OFF_CONFIG, VOUT_COMMAND and STORE_USER_ ALL. Individual fault bits can be cleared by writing a 1 to the respective bits in the STATUS registers. |

| 0x10 | Reserved, must be 0.                                                                                                                                                                                                                                                |

| 0x08 | Reserved, must be 0.                                                                                                                                                                                                                                                |

| 0x04 | Reserved, must be 0.                                                                                                                                                                                                                                                |

| 0x02 | Reserved, must be 0.                                                                                                                                                                                                                                                |

| 0x01 | Reserved, must be 0.                                                                                                                                                                                                                                                |

#### **MFR ADDRESS**

The MFR ADDRESS command byte and the ASEL pin set the 7 bits of the PMBus device address.

Setting this command to a value of 0x80 disables device addressing. The GLOBAL device address, 0x5A and 0x5B, cannot be deactivated. If the ASEL pin is floating or connected to  $V_{DD18}$ , the device will use the full MFR\_ADDRESS value. If a resistor is connected to the ASEL pin according to the table below, the four LSBs of the device address will be determined by the ASEL resistor value.

Reading MFR\_ADDRESS always returns the value loaded from EEPROM or written via PMBus write. The value read from MFR\_ADDRESS is not affected by the ASEL pin.

LT7182S does not ignore ASEL, even when bit 6 of MFR\_CONFIG\_ALL\_LT7182S is set to ignore the other resistor configuration pins. The three MSBs 6:4 of the device address are always determined by bits 6:4 of MFR\_ADDRESS.

| ASEL RESISTOR VALUE (±1%)     | VALUE OF PMBus DEVICE ADDRESS LSBs 3:0 |

|-------------------------------|----------------------------------------|

| Floating or V <sub>DD18</sub> | EEPROM value of MFR_ADDRESS            |

| 124kΩ                         | 0xF                                    |

| 107kΩ                         | 0xE                                    |

| 93.1kΩ                        | 0xD                                    |

| 80.6kΩ                        | 0xC                                    |

| 69.8kΩ                        | 0xB                                    |

| 60.4kΩ                        | 0xA                                    |

| 51.1kΩ                        | 0x9                                    |

| 43.2kΩ                        | 0x8                                    |

| 36.5kΩ                        | 0x7                                    |

| 30.9kΩ                        | 0x6                                    |

| 25.5kΩ                        | 0x5                                    |

| 21.0kΩ                        | 0x4                                    |

| 16.5kΩ                        | 0x3                                    |

| 11.8kΩ                        | 0x2                                    |

| 6.65kΩ                        | 0x1                                    |

| 0Ω (Grounded)                 | 0x0                                    |

#### Table 5. Illegal Addresses

| ADDRESS | USE                     |

|---------|-------------------------|

| OxOC    | ARA protocol address    |

| 0x37    | Zone write              |

| Ox5A    | Global all rail address |

| 0x5B    | Global address          |

Attempting to set this command to illegal values will set a CML invalid data fault. The current value of ASEL will be considered for this error check. During power on, if the MFR\_ADDRESS read from NVM and the current value of ASEL make an illegal address, the address will be set to 0x7C.

After changing the device address, leave at least 10µs for the new address to take effect before starting a new PMBus transaction.

The device will always respond to the global addresses 0x5A and 0x5B. Writes to address 0x5A will affect all pages, and reads will target page 0, as if PAGE == 0xFE.

#### MFR RAIL ADDRESS

The MFR\_RAIL\_ADDRESS command enables direct device address access to the currently selected channel. Writing this command sets the rail address for the currently selected channel. The value of this command should be common to all devices attached to a single power supply rail.

Setting this command to a value of 0x80 disables rail device addressing for the selected channel.

Attempting to set MFR\_RAIL\_ADDRESS to an illegal address, as defined above in MFR\_ADDRESS, will set a CML invalid data fault.

Writing PAGE\_PLUS\_READ or PAGE\_PLUS\_WRITE commands to the rail address will set a CML invalid command fault.

Reading from the rail address will result in a CML other fault.

After changing the a rail address, leave at least 10µs for the new address to take effect before starting a new PMBus transaction.

#### **GENERAL CONFIGURATION**

| COMMAND NAME            | CODE | DESCRIPTION                                   | TYPE     | PAGED | UNITS | NVM | DEFAULT                              |

|-------------------------|------|-----------------------------------------------|----------|-------|-------|-----|--------------------------------------|

| MFR_CHAN_CONFIG_LT7182S | 0xD0 | Configuration bits that are channel specific. | R/W Word | Y     |       | Y   | Ch. 0:<br>0x00D7<br>Ch. 1:<br>0x0057 |

| MFR_CONFIG_ALL_LT7182S  | 0xD1 | Configuration bits common to all channels.    | R/W Word | N     |       | Y   | 0x0100                               |

#### MFR\_CHAN\_CONFIG\_LT7182S

This command sets various global configuration bits.

Table 6. MFR\_CHAN\_CONFIG\_LT7182S Contents

|       | DEFAULT |       |                                                                                                                                                                                                                                                                                                               |

|-------|---------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BITS  | Ch O    | Ch 1  | MEANING                                                                                                                                                                                                                                                                                                       |

| 15-11 | 00000   | 00000 | Reserved                                                                                                                                                                                                                                                                                                      |

| 10    | 0       | 0     | 0 = PGOOD Pull down is disabled when VOUT_OV_FAULT_LIMIT is exceeded. 1 = PGOOD Pull down remains active when VOUT_OV_FAULT_LIMIT is exceeded.                                                                                                                                                                |

| 9     | 0       | 0     | 0 = PGOOD Pull down is disabled during output transitions. 1 = PGOOD Pull down is enabled during output transitions.                                                                                                                                                                                          |

| 8     | 0       | 0     | 0 = Default single phase application or polyphase leader operation. 1 = Polyphase follower mode. All but one channel in polyphase applications should be set to follower mode. Internal compensation cannot be used in polyphase operation. The channel operates in forced continuous conduction mode.        |

| 7     | 1       | 0     | 0 = Device will not pull SHARE_CLK down due to PVIN voltage level. 1 = Enable SHARE_CLK pull-down until PVIN exceeds VIN_ON, or if PVIN falls below VIN_OFF.                                                                                                                                                  |

| 6     | 1       | 1     | $0=250\Omega$ output pull-down is disabled.<br>$1=250\Omega$ output pull-down is enabled when off and during TOFF_FALL.                                                                                                                                                                                       |

| 5     | 0       | 0     | 0 = FAULT pin will be logged as a subevent when externally pulled low. 1 = FAULT pin will be logged as an event when externally pulled low.                                                                                                                                                                   |

| 4     | 1       | 1     | 0 = RUN will pulse low when OPERATION is written to turn off the channel. 1 = RUN will not pulse low when OPERATION is written to turn off the channel.                                                                                                                                                       |

| 3     | 0       | 0     | 0 = Disable detection of channel disabled for insufficient time to complete shutdown sequence. 1 = Enable detection of channel disabled for insufficient time to complete shutdown sequence. See note 2 below.                                                                                                |

| 2     | 1       | 1     | 0 = Channel output is remains active if SHARE_CLK is held low. 1 = Channel output is disabled if SHARE_CLK is held low.                                                                                                                                                                                       |

| 1     | 1       | 1     | 0 = If FAULT pin is externally asserted, it will be logged and STATUS_MFR_SPECIFIC bit 0 will be set 1 = If FAULT# pin is externally asserted, it will not be logged and STATUS_MFR_SPECIFIC bit 0 will not be set. As a consequence, the ALERT pin is also not asserted due to FAULT pin external assertion. |

| 0     | 1       | 1     | 0 = VOUT must be below MFR_DISCHARGE_THRESHOLD for the device to allow the channels to be enabled. 1 = Output may be enabled, regardless of VOUT.                                                                                                                                                             |

**Note 1:** (bit 4). When this bit is cleared to a 0, the RUN pin will be pulled down whenever the channel is commanded off with the OPERATION command for a duration set by MFR\_RESTART\_DELAY.

**Note 2:** (bit 3). A Short Shutdown Cycle event occurs whenever the channel is turned off and commanded back on before the TOFF\_DELAY plus TOFF\_FALL time has elapsed. If a Short Shutdown Cycle event occurs and bit 3 of MFR\_CHAN\_CONFIG\_LT7182S is set to a 1, the output rail will stop delivering power immediately and restart with a 20µs delay. If the Short Shutdown Cycle event occurs and this bit is set to a 0, the TOFF\_DELAY plus TOFF\_FALL times will be honored as a normal sequence off event, and the part will restart after an additional 20µs delay.

Note 3: (bit 8) When bit 6 of MFR\_CONFIG\_ALL\_LT7182S is 0, configuration resistors may override the stored NVM value for this bit at power-up.

## MFR\_CONFIG\_ALL\_LT7182S

This command sets various global configuration bits.

Table 7. MFR\_CONFIG\_ALL\_LT7182S Contents

| BITS | DEFAULT | MEANING                                                                                                                                                                                                                                                                                                                                              |

|------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15-9 | 0000000 | Reserved                                                                                                                                                                                                                                                                                                                                             |

| 8    | 1       | 0 = Linear11 and ULinear16 formats selected, depending on the command. 1 = IEEE half-precision floating point format selected.                                                                                                                                                                                                                       |

| 7    | 0       | 0 = Fault log is disabled1 = Fault log is enabled                                                                                                                                                                                                                                                                                                    |

| 6    | 0       | 0 = Configuration resistors will be measured and used to configure the device during initialization1 = CFG pin configuration resistors will be ignored on pins VOUTO_CFG, VOUT1_CFG/POLYPHASE_CONFIG, and SYNC/PWM_CFG. Note that ASEL cannot be ignored and is always measured during initialization and used for device address (see MFR_ADDRESS). |

| 5    | 0       | 0 = Enable CML fault for quick command read message. See note 1 below. 1 = Disable CML fault for quick command read message.                                                                                                                                                                                                                         |

| 4    | 0       | Reserved                                                                                                                                                                                                                                                                                                                                             |

| 3    | 0       | Reserved                                                                                                                                                                                                                                                                                                                                             |

| 2    | 0       | 0 = Valid PEC not required1 = Valid PEC required                                                                                                                                                                                                                                                                                                     |

| 1    | 0       | 0 = Disable PMBus clock stretching. If device is too busy to process a command, the device will NACK the command and set bit 7 in STATUS_BYTE and STATUS_WORD1 = Enable PMBus clock stretching.                                                                                                                                                      |

| 0    | 0       | 0 = When a channel is enabled, only the status bits affecting that channel will be cleared, including global status bits 1 = All fault and warning status bits will be cleared with either channel is enabled.                                                                                                                                       |

**Note 1:** (bit 5). The PMBus specification indicates that PMBus devices should indicate a fault has occurred if a command starts with the read bit set in the address byte. When bit 5 of MFR\_CONFIG\_ALL\_LT7182S is set, this device will not indicate a fault.

Table 8. On, Off and Margin

| COMMAND NAME  | CODE | DESCRIPTION                                                 | TYPE      | PAGED | UNITS | NVM | DEFAULT |

|---------------|------|-------------------------------------------------------------|-----------|-------|-------|-----|---------|

| OPERATION     | 0x01 | Operating mode control. On/off, margin high and margin low. | R/W Byte  | Υ     |       | Υ   | 0x80    |

| ON_OFF_CONFIG | 0x02 | RUN pin and PMBus OPERATION command configuration.          | R/W Byte  | Υ     |       | Υ   | 0x1E    |

| MFR_RESET     | 0xFD | Commanded reset.                                            | Send Byte | N     |       |     |         |

#### **OPERATION**

The OPERATION command is used to turn the channels on or off in conjunction with the RUN pins, based on the configuration defined in ON\_OFF\_CONFIG. It is also used to set the output voltage to VOUT\_MARGIN\_HIGH or VOUT\_MARGIN\_LOW.

Disabling and then reenabling a channel will cause all latched faults and status bits to be cleared for that channel. Overtemperature and internal reference faults are shared between both channels. Disabling and then reenabling either channel will clear the latched condition for overtemperature and internal reference faults for both channels.

The table below shows the values of OPERATION supported by the LT7182S.

| FUNCTION             | VALUE |

|----------------------|-------|

| Turn off immediately | 0x00  |

| Turn on              | 0x80  |

| Margin low           | 0x98  |

| Margin high          | 0xA8  |

| Sequence off         | 0x40  |

#### ON OFF CONFIG

The ON\_OFF\_CONFIG command configures the combination of RUN pin input and serial bus commands required to turn the channel on and off.

The only bits allowed to be changed are as follows:

- 3: When high, the channel will only provide output power if the on/off portion of OPERATION is set.

- 2: When high, the channel will only provide output power if the corresponding RUN pin is high.

- 0: When high, the channel will perform an immediate shutdown when the RUN pin is de-asserted. Bit 0 only has an effect when bit 2 is also set.

Bits 4 and 1 must both be 1. Setting bits 4 or 1 to 0 will generate a CML fault.

If ON\_OFF\_CONFIG bits 2 and 3 are both set to 1 (which is the factory default), the channel will only turn on if the RUN pin is high and the OPERATION command is set to enable (on, margin low, or margin high).

#### MFR\_RESET

Causes the device to reset.

#### PWM CONFIGURATION

| COMMAND NAME            | CODE | DESCRIPTION                          | TYPE     | PAGED | UNITS   | NVM | DEFAULT                   |

|-------------------------|------|--------------------------------------|----------|-------|---------|-----|---------------------------|

| FREQUENCY_SWITCH        | 0x33 | Controller switching frequency       | R/W Word | N     | kHz     | Υ   | 1000.0                    |

| MFR_PWM_MODE_LT7182S    | 0xD4 | Paged PWM config, including PWM mode | R/W Word | Υ     |         | Υ   | 0x1DD4                    |

| MFR_PWM_PHASE_LT7182S   | 0xF5 | Set PWM phase                        | R/W Word | Y     | Degrees | Y   | Ch. 0: 0.0<br>Ch 1: 180.0 |

| MFR_SYNC_CONFIG_LT7182S | 0xF6 | SYNC pin config for all pages        | R/W Byte | N     |         | Υ   | 0x00                      |

#### FREQUENCY SWITCH

The FREQUENCY\_SWITCH command selects the internal oscillator frequency in 100kHz steps. The valid range is 400kHz to 4MHz. The FREQUENCY\_SWITCH value must be a multiple of 100kHz.

Regardless of the value of FREQUENCY\_SWITCH, if external clock is present on the SYNC/PWM\_CFG pin, the LT7182S will attempt to synchronize the PWM to the external clock, unless bit 1 or 0 in MFR\_SYNC\_CONFIG\_LT7182S is set. If an external clock is to be used for synchronization, it is recommended to program FREQUENCY\_SWITCH to the same frequency as the external clock.

This command has two data bytes encoded in either Linear11 or half-precision floating point format, as selected by MFR\_CONFIG\_ALL\_LT7182S bit 8.

#### MFR PWM MODE LT7182S

#### Table 9. MFR\_PWM\_MODE\_LT7182S Contents

| BITS  | DEFAULT | MEANING         |                                                        | ·                                                                                |

|-------|---------|-----------------|--------------------------------------------------------|----------------------------------------------------------------------------------|

| 15:14 | 0b00    | Must be 0.      |                                                        |                                                                                  |

| 13:11 | 0b011   | Error Amplifier | Transconductance (GMEA)                                |                                                                                  |

|       |         | Value           | Standard Mode<br>(MFR_PWM_MODE_LT7182S Bit 1 Set to 0) | High-Performance Low-V <sub>OUT</sub> Mode (MFR_PWM_MODE_LT7182S Bit 1 Set to 1) |

|       |         | 7               | 300μS                                                  | 1.2mS                                                                            |

|       |         | 6               | 262.5μS                                                | 1.05mS                                                                           |

|       |         | 5               | 225μS                                                  | 900μS                                                                            |

|       |         | 4               | 187.5µS                                                | 750μS                                                                            |

|       |         | 3               | 150μS                                                  | 600µS                                                                            |

|       |         | 2               | 112.5µS                                                | 450μS                                                                            |

|       |         | 1               | 75μS                                                   | 300μS                                                                            |

|       |         | 0               | 37.5μS                                                 | 150µS                                                                            |

## MFR\_PWM\_MODE\_LT7182\$

#### Table 9. MFR PWM MODE LT7182S Contents

| BITS | DEFAULT | MEANING                    |                                                                              |                                                          |

|------|---------|----------------------------|------------------------------------------------------------------------------|----------------------------------------------------------|

| 10:9 | 0b10    | I <sub>LIM</sub> Range (Cu | rrent Limit Selection)                                                       |                                                          |

|      |         | Value                      | Positive Valley Current Limit I <sub>LIM-POS</sub> (Typ)                     | Negative Valley Current Limit I <sub>LIM-NEG</sub> (Typ) |

|      |         | 3                          | 8.5A                                                                         | -4.25A                                                   |

|      |         | 2                          | 6.5A                                                                         | <b>−4A</b>                                               |

|      |         | 1                          | 4.5A                                                                         | -3.4A                                                    |

|      |         | 0                          | 3.0A                                                                         | -2.3A                                                    |

| 8:6  | 0b111   | Internal Compe             | nsation Capacitor Value C <sub>ITH</sub>                                     |                                                          |

|      |         | Value                      | C <sub>ITH</sub> Capacitor Value                                             |                                                          |

|      |         | 7                          | 80pF                                                                         |                                                          |

|      |         | 6                          | 70pF                                                                         |                                                          |

|      |         | 5                          | 60pF                                                                         |                                                          |

|      |         | 4                          | 50pF                                                                         |                                                          |

|      |         | 3                          | 40pF                                                                         |                                                          |

|      |         | 2                          | 30pF                                                                         |                                                          |

|      |         | 1                          | 20pF                                                                         |                                                          |

|      |         | 0                          | 10pF                                                                         |                                                          |

| 5:3  | 0b010   | Internal compe             | nsation lead resistor value R <sub>ITH</sub>                                 |                                                          |

|      |         | Value                      | R <sub>ITH</sub> Resistor Value                                              |                                                          |

|      |         | 7                          | 120kΩ                                                                        |                                                          |

|      |         | 6                          | 100kΩ                                                                        |                                                          |

|      |         | 5                          | 80kΩ                                                                         |                                                          |

|      |         | 4                          | 60kΩ                                                                         |                                                          |

|      |         | 3                          | 40kΩ                                                                         |                                                          |

|      |         | 2                          | 20kΩ                                                                         |                                                          |

|      |         | 1                          | 10kΩ                                                                         |                                                          |

|      |         | 0                          | 5kΩ                                                                          |                                                          |

| 2    | 1       | 0 = Bit 0 will be          | used during TOFF_FALL.                                                       |                                                          |

|      |         |                            | continuous mode during TOFF_FALL regardless of the                           |                                                          |

| 1    | 0       |                            | h-performance, low-V <sub>OUT</sub> mode. Full V <sub>OUT</sub> range availa |                                                          |

|      | 1       |                            | n-performance, low-V <sub>OUT</sub> mode. V <sub>OUT</sub> limited to 1.375. |                                                          |

| 0    | 0       | voltage, and du            | erates in forced continuous conduction mode when the ring TOFF_FALL.         | e output is in regulation at the commanded output        |